# Manonmaniam Sundaranar University, Directorate of Distance & Continuing Education, Tirunelyeli - 627 012 Tamilnadu, India

# OPEN AND DISTANCE LEARNING(ODL) PROGRAMMES

(FOR THOSE WHO JOINED THE PROGRAMMES FROM THE ACADEMIC YEAR 2023–2024)

# III YEAR B.Sc. Physics Course Material Digital Electronics And Microprocessor 8085

# **Prepared**

By

Dr. S. Shailajha

Dr. P. Hema

Assistant Professor

Department of Physics

Manonmaniam Sundaranar University

Tirunelyeli – 12

#### DIGITAL ELECTRONICS AND MICROPROCESSOR 8085

UNIT-I: DECIMAL, BINARY, OCTAL, HEXA DECIMAL NUMBERS SYSTEMS AND THEIR CONVERSIONS – CODES: BCD, Gray and excess-3 codes – code conversions – binary addition, binary subtraction using 1's & 2's complement methods – Boolean laws – De-Morgan's theorem – basic logic gates – universal logic gates (NAND & NOR) – standard representation of logic functions (SOP & POS) – minimization techniques (Karnaugh map: 2, 3, 4 variables).

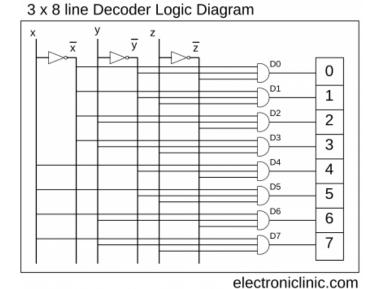

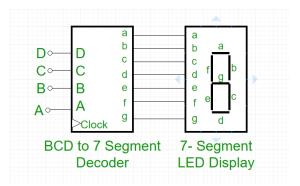

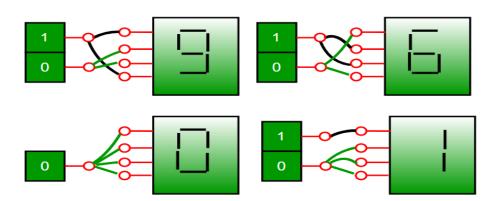

**UNIT-II: ADDERS**: half & full adder – subtractors: half & full subtractor – parallel binary adder – magnitude comparator – multiplexers (4:1) & demultiplexers (1:4), encoder (8-line to 3-line) and decoder (3-line to 8-line), BCD to seven segment decoders.

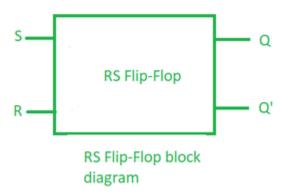

**UNIT-III: FLIP-FLOPS**: R-S Flip-flop, J-K Flip-Flop, T and D type flip-flops, master-slave flip-flop, truth tables, registers: serial in serial out and parallel in and parallel out – counters asynchronous: mod-8, mod-10, synchronous – ring counter and up-down counter – A/D and D/A converter.

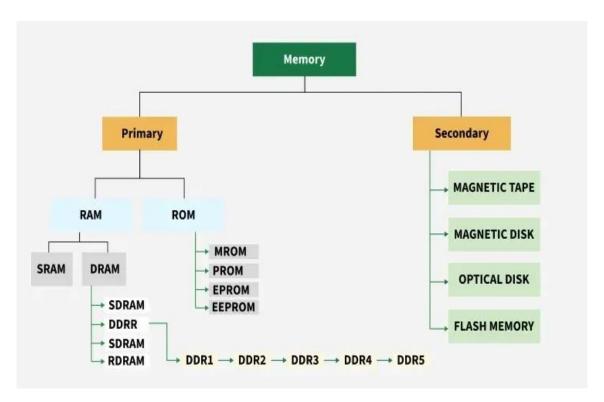

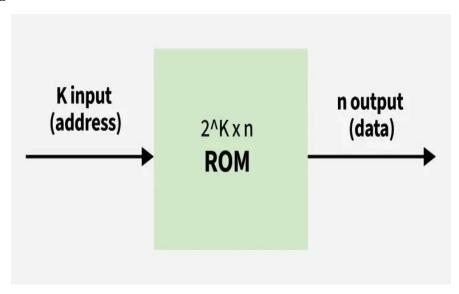

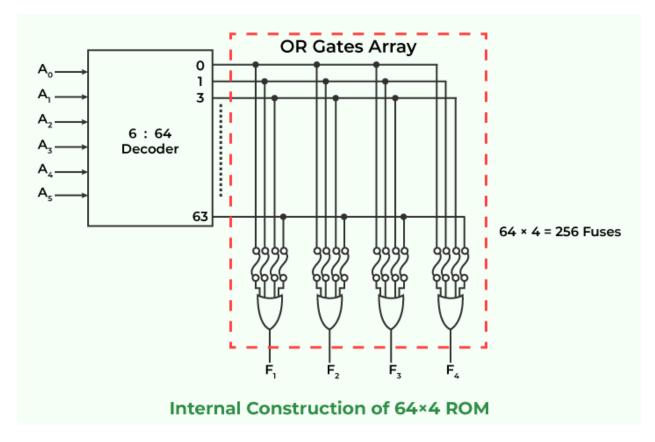

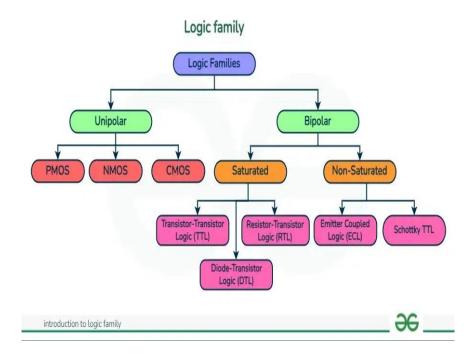

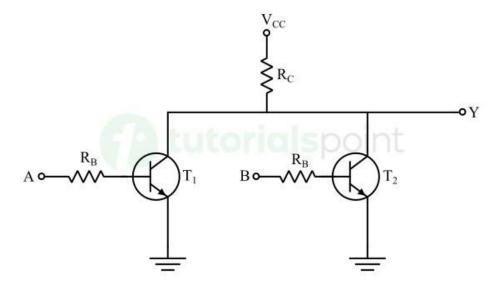

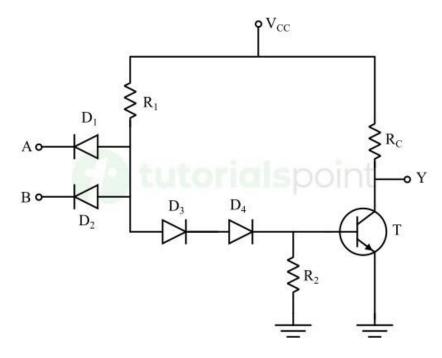

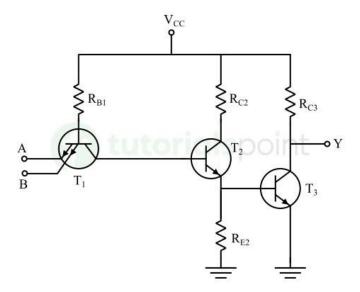

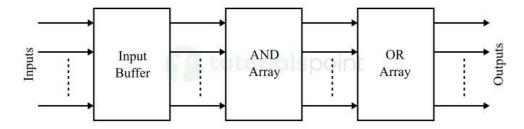

UNIT-IV: GENERAL MEMORY OPERATIONS: ROM, RAM (static and dynamic), PROM, EPROM, EEPROM, EAROM. IC-logic families: RTL, DTL, TTL logic, CMOS NAND & NOR Gates, CMOS Inverter. Programmable Logic Devices – Programmable Logic Array (PLA), Programmable Array Logic (PAL).

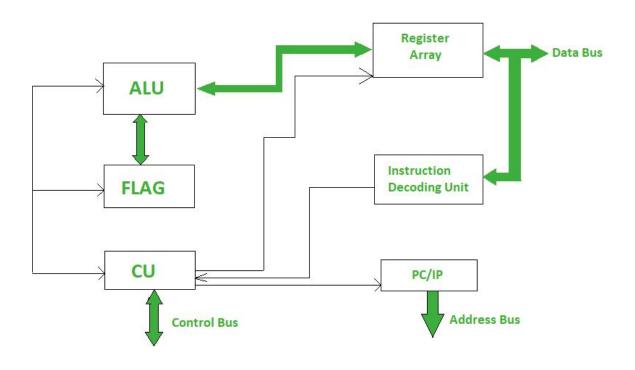

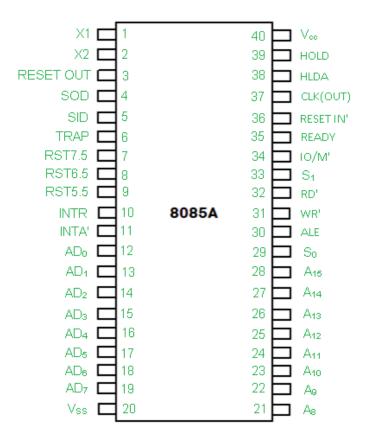

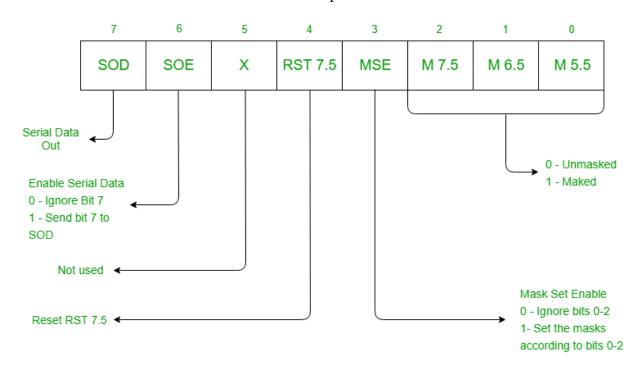

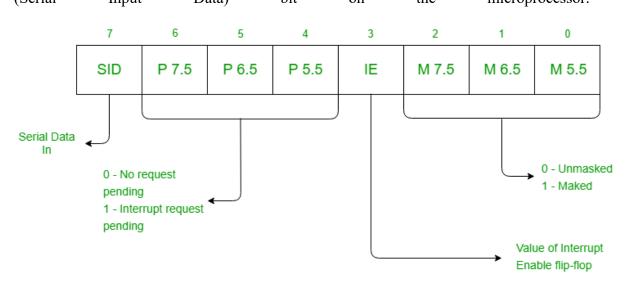

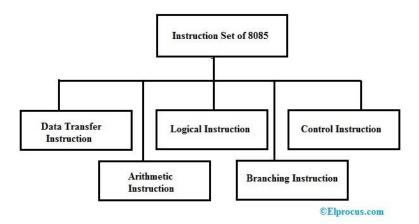

UNIT-V:8085 MICROPROCESSOR: Introduction to microprocessor – pin configuration of 8085 – Flags – Registers (General and special purpose) – interrupts and its priority – instruction set of 8085 – addressing modes of 8085 – Assembly language programming using 8085 – programs for addition, subtraction, multiplication and division (8-Bit only).

#### **TEXTBOOKS**

- 1. M. Morris Mano Digital Design-3rd Edition, PHI, New Delhi.

- 2. Ronald J. Tocci Digital Systems-Principles and Applications 6/e, PHI, New Delhi. 1999. (UNITS 1 to IV)

- 3. S. Salivahana & S. Arivazhagan-Digital circuits and design

- 4. Microprocessor Architecture, Programming and Applications with the 8085-Penram International Publishing, Mumbai-Ramesh S. Gaonkar

- 5. Microcomputer Systems the 8086/8088 family-YU-Cheng Liu and Glenn A.

# **UNIT-I:**

**DECIMAL, BINARY, OCTAL, HEXA DECIMAL NUMBERS SYSTEMS AND THEIR CONVERSIONS** – **CODES**: BCD, Gray and excess-3 codes – code conversions – binary addition, binary subtraction using 1's & 2's complement methods – Boolean laws – De-Morgan's theorem – basic logic gates – universal logic gates (NAND & NOR) – standard representation of logic functions (SOP & POS) – minimization techniques (Karnaugh map: 2, 3, 4 variables).

# 1.1. Number Systems:

A digital number system is a positional number system that has some symbols called digits. It provides a complete set of digits, operators, and rules to perform operations. In a digital number system, the number of digits used determines the base of the number system. For example, the binary number system has two digits (0 and 1), hence, the base of the binary number system is 2. Digital number systems form the foundation of the modern computing technologies and digital electronics. They are used to represent, process, and manipulate the information using a digital system.

# **Types of Digital Number Systems:**

In digital electronics, the following four types of digital number systems are mainly used

- Binary Number System

- Decimal Number System

- Octal Number System

- Hexadecimal Number System

# **Binary Number System:**

Binary number system is the fundamental building block behind the implementation and working of all digital systems. Binary number system has two symbols or digits, i.e., 0 and 1.

Hence, these two digits are used to represent information and perform all the digital operations. Each binary digit is called a bit. Since there are two digits are used in the binary number system, hence its base is 2. Therefore, the value of a binary number is calculated as the sum of powers of 2. Binary digits are used in digital system to represent their ON and OFF states. Where, 0 is used to represent the OFF state of the digital system and 1 is used to represent the ON state of the system. Overall, the binary number system forms the foundation of computation, digital communication, and digital information storage.

#### **Example**

Consider the binary number 1101.011. The integer part of this number is 1101 and the fractional part of this number is 0.011. The digits 1, 0, 1 and 1 of the integer part have weights of  $2^0$ ,  $2^1$ ,  $2^2$ ,  $2^3$  respectively. Similarly, the digits 0, 1 and 1 of fractional part have weights of  $2^{-1}$ ,  $2^{-2}$ ,  $2^{-3}$  respectively.

Mathematically, we can write it as,

$$1101.011 = (1 \times 2^3) + (1 \times 2^2) + (0 \times 2^1) + (1 \times 2^0) + (0 \times 2^{-1}) + (1 \times 2^{-2}) + (1 \times 2^{-3})$$

After simplifying the right-hand side terms, we will get a decimal number, which is an equivalent of binary number on left-hand side.

# **Decimal Number System:**

Decimal number system is not inherently a digital number system. But it is widely used to represent the digital information in a human readable format. Decimal number system is a base 10 number system having 10 unique digits i.e., 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9. It is the standard number system used by human beings to represent information in a natural way. However, a digital system cannot directly process the information represented in decimal form, so it is converted into binary form and then processed. The base of the decimal number system is 10. So, the value of a decimal number is calculated by the sum of powers of 10.

#### **Example:**

Consider the decimal number 1358.246. The integer part of this number is 1358 and the fractional part of this number is 0.246. The digits 8, 5, 3 and 1 have weights of  $(10)^0$ ,  $(10)^1$ ,  $(10)^2$  and  $(10)^3$  respectively. Similarly, the digits 2, 4 and 6 have weights of  $(10)^{-1}$ ,  $(10)^{-2}$  and  $(10)^{-3}$  respectively.

Mathematically, we can write it as,

$$1358.246 = (1 \times 10^{3}) + (3 \times 10^{2}) + (5 \times 10^{1}) + (8 \times 10^{0}) + (2 \times 10^{-1}) + (4 \times 10^{-2}) + (6 \times 10^{-3})$$

After simplifying the right-hand side terms, we will get the decimal number, which is on the left-hand side.

# **Octal Number System:**

The octal number system is another type of digital number system used in the field of digital electronics to represent information. It is a base 8 number system having eight unique digits i.e., 0, 1, 2, 3, 4, 5, 6, and 7. It is important note that the octal number system is equivalent to 3-bit binary number system as  $2^3 = 8$ . Hence, this number system can be used in computing and digital electronic applications. The value of an octal number is obtained by the sum of powers of 8, as 8 is the base of the octal number system. Octal number system is used in the field of digital electronics to represent binary information in compact form, permissions in Linux or Unix systems, IPv6 address, binary machine code instructions, in error detection algorithms, etc.

# **Example:**

Consider the octal number 1457.236. Integer part of this number is 1457 and fractional part of this number is 0.236. The digits 7, 5, 4 and 1 have weights of  $(8)^0$ ,  $(8)^1$ ,  $(8)^2$  and  $(8)^3$  respectively. Similarly, the digits 2, 3 and 6 have weights of  $(8)^{-1}$ ,  $(8)^{-2}$ ,  $(8)^{-3}$  respectively.

Mathematically, we can write it as,

$$1457.236 = (1 \times 8^3) + (4 \times 8^2) + (5 \times 8^1) + (7 \times 8^0) + (2 \times 8^{-1}) + (3 \times 8^{-2}) + (6 \times 8^{-3})$$

After simplifying the right-hand side terms, we will get a decimal number, which is an equivalent of octal number on the left-hand side.

#### **Hexadecimal Number System:**

The hexadecimal number system is a base 16 number system. It has 16 digits, 0 to 9 and A to F. Where, A represents 10, B represents 11, C represents 12, D represents 13, E represents 14, and F represents 15. The hexadecimal number system is equivalent to a 4-bit binary number system as  $2^4 = 16$ . Thus, the value of a hexadecimal number can be calculated by the sum of powers of 16. In the field of digital electronics, the hexadecimal number system is used in memory address representation, digital colors representation, low level computer programming, encoding, assembly language programming, microcontrollers, keyboards, etc. Hexadecimal number system creates a balance between digital representation and human readability.

#### **Example:**

Consider the hexadecimal number 1A05.2C4. The integer part of this number is 1A05 and the fractional part of this number is 0.2C4. The digits 5, 0, A and 1 have weights of  $(16)^0$ ,  $(16)^1$ ,  $(16)^2$  and  $(16)^3$  respectively. Similarly, the digits 2, C and 4 have weights of  $(16)^{-1}$ ,  $(16)^{-2}$  and  $(16)^{-3}$  respectively.

Mathematically, we can write it as,

$$1A05.2C4 = (1 \times 16^3) + (10 \times 16^2) + (0 \times 16^1) + (5 \times 16^0) + (2 \times 16^{-1}) + (12 \times 16^{-2}) + (4 \times 16^{-3})$$

After simplifying the right-hand side terms, we will get a decimal number, which is an equivalent of the hexadecimal number on the left-hand side.

# **Binary Coded Decimal (BCD):**

The binary coded decimal (BCD) is a type of binary code used to represent a given decimal number in an equivalent binary form. BCD-to-decimal and decimal-to-BCD conversions are very easy and straightforward. The BCD equivalent of a decimal number is written by replacing each decimal digit in the integer and fractional parts with its four-bit binary equivalent. As an example, the BCD equivalent of (23.15)<sub>10</sub> is written as (0010 0011.0001 0101)<sub>BCD</sub>. The BCD code is more precisely known as the 8421 BCD code, with 8, 4, 2 and 1 representing the weights of different bits in the four-bit groups, starting from MSB and proceeding towards LSB. This feature makes it a weighted code, which means that each bit in the four-bit group representing a given decimal digit has an assigned weight.

**Table 1.1 BCD codes**

| Decimal | 8421BCD code | 4221 BCD code | 5421 BCD code |

|---------|--------------|---------------|---------------|

| 0       | 0000         | 0000          | 0000          |

| 1       | 0001         | 0001          | 0001          |

| 2       | 0010         | 0010          | 0010          |

| 3       | 0011         | 0011          | 0011          |

| 4       | 0100         | 1000          | 0100          |

| 5       | 0101         | 0111          | 1000          |

| 6       | 0110         | 1100          | 1001          |

| 7       | 0111         | 1101          | 1010          |

| 8       | 1000         | 1110          | 1011          |

| 9       | 1001         | 1111          | 1100          |

Other weighted BCD codes include the 4221 BCD and 5421 BCD codes. Again, 4, 2, 2 and 1 in the 4221 BCD code and 5, 4, 2 and 1 in the 5421 BCD code represent weights of the relevant bits. Table 1.1 shows a comparison of 8421, 4221 and 5421 BCD codes. As an example, (98.16)<sub>10</sub> will be written as 1111 1110.0001 1100 in 4221 BCD code and 1100 1011.0001 1001 in 5421 BCD code. Since the 8421 code is the most popular of all the BCD codes, it is simply referred to as the BCD code.

# **Gray Code:**

The Gray code was designed by Frank Gray at Bell Labs and patented in 1953. It is an un weighted binary code in which two successive values differ only by 1 bit. Owing to this feature, the maximum error that can creep into a system using the binary gray code to encode data is much less than the worst-case error encountered in the case of straight binary encoding. Table 1.2 lists the binary and gray code equivalents of decimal numbers 0–15. An examination of the four-bit gray code numbers, as listed in Table 1.2, shows that the last entry rolls over to the first entry. That is, the last and the first entry also differ by only 1 bit. This is known as the cyclic property of the gray code. Although there can be more than one gray code for a given word length, the term was first applied to a specific binary code for non-negative integers and called the binary-reflected gray code or simply the gray code.

Table 1.2 Gray code

| Decimal | Binary | Gray | Decimal | Binary | Gray |

|---------|--------|------|---------|--------|------|

| 0       | 0000   | 0000 | 8       | 1000   | 1100 |

| 1       | 0001   | 0001 | 9       | 1001   | 1101 |

| 2       | 0010   | 0011 | 10      | 1010   | 1111 |

| 3       | 0011   | 0010 | 11      | 1011   | 1110 |

| 4       | 0100   | 0110 | 12      | 1100   | 1010 |

| 5       | 0101   | 0111 | 13      | 1101   | 1011 |

| 6       | 0110   | 0101 | 14      | 1110   | 1001 |

| 7       | 0111   | 0100 | 15      | 1111   | 1000 |

# **Excess-3 codes:**

The excess-3 code is another important BCD code. It is particularly significant for arithmetic operations as it overcomes the shortcomings encountered while using the 8421 BCD code to add two decimal digits whose sum exceeds 9. The excess-3 code has no such limitation, and it considerably simplifies arithmetic operations.

| Decimal number | Excess-3 code | Decimal number | Excess-3 code |

|----------------|---------------|----------------|---------------|

| 0              | 0011          | 5              | 1000          |

| 1              | 0100          | 6              | 1001          |

| 2              | 0101          | 7              | 1010          |

| 3              | 0110          | 8              | 1011          |

| 4              | 0111          | 9              | 1100          |

Table 1.3 Excess-3 code equivalent of decimal numbers.

Table 1.3 lists the excess-3 code for the decimal numbers 0–9. The excess-3 code for a given decimal number is determined by adding '3' to each decimal digit in the given number and then replacing each digit of the newly found decimal number by its four-bit binary equivalent. It may be mentioned here that, if the addition of '3' to a digit produces a carry, as is the case with the digits 7, 8 and 9, that carry should not be taken forward. The result of addition should be taken as a single entity and subsequently replaced with its excess-3 code equivalent. As an example, let us find the excess-3 code for the decimal number 597:

- The addition of '3' to each digit yields the three new digits/numbers '8', '12' and '10'.

- The corresponding four-bit binary equivalents are 1000, 1100 and 1010 respectively.

- The excess-3 code for 597 is therefore given by: 1000 1100 1010=100011001010.

Also, it is normal practice to represent a given decimal digit or number using the maximum number of digits that the digital system is capable of handling. For example, in four-digit decimal arithmetic, 5 and 37 would be written as 0005 and 0037 respectively. The corresponding 8421 BCD equivalents would be 0000000000000101 and 0000000000110111 and the excess-3 code equivalents would be 0011001100111000 and 0011001101101010.

Corresponding to a given excess-3 code, the equivalent decimal number can be determined by first splitting the number into four-bit groups, starting from the radix point, and then subtracting 0011 from each four-bit group. The new number is the 8421 BCD equivalent of the given excess-3 code, which can subsequently be converted into the equivalent decimal number.

As an example, following these steps, the decimal equivalent of excess-3 number 01010110.10001010 would be 23.57.

Another significant feature that makes this code attractive for performing arithmetic operations is that the complement of the excess-3 code of a given decimal number yields the excess-3 code for 9's complement of the decimal number. As adding 9's complement of a decimal number B to a decimal number A achieves A - B, the excess-3 code can be used effectively for both addition and subtraction of decimal numbers.

#### 1.2. Code conversions:

# 1. BCD-to-Binary Conversion:

A given BCD number can be converted into an equivalent binary number by first writing its decimal equivalent and then converting it into its binary equivalent. The first step is straightforward, and the second step was explained in the previous chapter. As an example, we will find the binary equivalent of the BCD number 0010 1001.0111 0101:

- BCD number: 0010 1001.0111 0101.

- Corresponding decimal number: 29.75.

- The binary equivalent of 29.75 can be determined to be 11101 for the integer part and .11 for the fractional part.

- Therefore,  $(0010\ 1001.0111\ 0101)\ BCD = (11101.11)2$ .

# 2. Binary-to-BCD Conversion

The process of binary-to-BCD conversion is the same as the process of BCD-to-binary conversion executed in reverse order. A given binary number can be converted into an equivalent BCD number by first determining its decimal equivalent and then writing the corresponding BCD equivalent. As an example, we will find the BCD equivalent of the binary number 10101011.101:

- The decimal equivalent of this binary number can be determined to be 171.625.

- The BCD equivalent can then be written as 0001 0111 0001.0110 0010 0101.

# 3. Binary-Gray Code Conversion:

A given binary number can be converted into its Gray code equivalent by going through the following:

#### steps:

- 1. Begin with the most significant bit (MSB) of the binary number. The MSB of the Gray code equivalent is the same as the MSB of the given binary number.

- 2. The second most significant bit, adjacent to the MSB, in the Gray code number is obtained by adding the MSB and the second MSB of the binary number and ignoring the carry, if any. That is, if the MSB and the bit adjacent to it are both '1', then the corresponding Gray code bit would be a '0'.

- 3. The third most significant bit, adjacent to the second MSB, in the Gray code number is obtained by adding the second MSB and the third MSB in the binary number and ignoring the carry, if any.

- 4. The process continues until we obtain the LSB of the Gray code number by the addition of the LSB and the next higher adjacent bit of the binary number. The conversion process is further illustrated with the help of an example showing step-by-step conversion of (1011)<sub>2</sub> into its Gray code equivalent:

Binary 1011

Gray code 1---

Binary 1011

Gray code 11--

Binary 1011

Gray code 111-

Binary 1011

Gray code 1110

# 4. Gray Code-Binary Conversion:

A given Gray code number can be converted into its binary equivalent by going through the following steps:

- 1. Begin with the most significant bit (MSB). The MSB of the binary number is the same as the MSB of the Gray code number.

- 2. The bit next to the MSB (the second MSB) in the binary number is obtained by adding the MSB in the binary number to the second MSB in the Gray code number and disregarding the carry, if any.

- 3. The third MSB in the binary number is obtained by adding the second MSB in the binary number to the third MSB in the Gray code number. Again, carry, if any, is to be ignored.

- 4. The process continues until we obtain the LSB of the binary number.

The conversion process is further illustrated with the help of an example showing step-by-step conversion of the Gray code number 1110 into its binary equivalent:

Gray code 1110

Binary 1---

Gray code 1110

Binary 10 - -

Gray code 1110

Binary 101

Gray code 1110

Binary 1011

# 1.3. Binary addition, Binary subtraction using 1's & 2's complement methods:

# **Basic Rules of Binary Addition and Subtraction:**

The basic principles of binary addition and subtraction are similar to what we all know so well in the case of the decimal number system. In the case of addition, adding '0' to a certain digit produces the same digit as the sum, and, when we add '1' to a certain digit or number in the decimal number system, the result is the next higher digit or number, as the case may be. For example, 6 + 1 in decimal equals '7' because '7' immediately follows '6' in the decimal number system. Also, 7 + 1 in octal equals '10' as, in the octal number system, the next adjacent higher

number after '7' is '10'. Similarly, 9 + 1 in the hexadecimal number system is 'A'. With this background, we can write the basic rules of binary addition as follows:

- 1.0+0=0.

- 2.0 + 1 = 1.

- 3.1 + 0 = 1.

- 4. 1 + 1 = 0 with a carry of '1' to the next more significant bit.

- 5. 1 + 1 + 1 = 1 with a carry of '1' to the next more significant bit.

Table 1.4 summarizes the sum and carry outputs of all possible three-bit combinations. We have taken three-bit combinations as, in all practical situations involving the addition of two larger bit

$\mathbf{A}$ B Carry-Carry-B Carry-Sum Carry-Sum A in(C<sub>in</sub>) out C<sub>0</sub>) in(C<sub>in</sub>) out(C<sub>0</sub>) 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 0 1 1 1 1 1 1

Table 1.4 Binary addition of three bits

numbers, we need to add three bits at a time. Two of the three bits are the bits that are part of the two binary numbers to be added, and the third bit is the carry-in from the next less significant bit column. The basic principles of binary subtraction include the following:

- 1.0-0=0.

- 2.1 0 = 1.

- 3.1 1 = 0.

- 4.0 1 = 1 with a borrow of 1 from the next more significant bit.

The above-mentioned rules can also be explained by recalling rules for subtracting decimal numbers. Subtracting '0' from any digit or number leaves the digit or number unchanged. This explains the first two rules. Subtracting '1' from any digit or number in decimal produces the

immediately preceding digit or number as the answer. In general, the subtraction operation of larger-bit binary numbers also involves three bits, including the two bits involved in the subtraction, called the minuend (the upper bit) and the subtrahend (the lower bit), and the borrow-in. The subtraction operation produces the difference output and borrow-out, if any. Table 1.5 summarizes the binary subtraction operation. The entries in Table 1.5 can be explained by recalling the basic rules of binary subtraction mentioned above, and that the subtraction operation involving three bits, that is, the minuend (A), the subtrahend (B) and the borrow-in (B<sub>in</sub>), produces a difference output equal to  $(A - B - B_{in})$ . It may be mentioned here that, in the case of subtraction of larger-bit binary numbers, the least significant bit column always involves two bits to produce a difference output bit and the borrow-out bit. The borrow-out bit produced here becomes the borrow-in bit for the next more significant bit column, and the process continues until we reach the most significant bit column.

**Table 1.5 Binary subtraction**

|            | Inputs     |            |            | ts         |

|------------|------------|------------|------------|------------|

| Minuend    | Subtrahend | Borrow-in  | Difference | Borrow-out |

| <b>(A)</b> | <b>(B)</b> | $(B_{in})$ | <b>(D)</b> | $(B_0)$    |

| 0          | 0          | 0          | 0          | 0          |

| 0          | 0          | 1          | 1          | 1          |

| 0          | 1          | 0          | 1          | 1          |

| 0          | 1          | 1          | 0          | 1          |

| 1          | 0          | 0          | 1          | 0          |

| 1          | 0          | 1          | 0          | 0          |

| 1          | 1          | 0          | 0          | 0          |

| 1          | 1          | 1          | 1          | 1          |

# **Addition of Larger-Bit Binary Numbers:**

The addition of larger binary integers, fractions or mixed binary numbers is performed column wise in just the same way as in the case of decimal numbers. In the case of binary

numbers, however, we follow the basic rules of addition of two or three binary digits, as outlined earlier. The process of adding two larger-bit binary numbers can be best illustrated with the help of an example.

Consider two generalized four-bit binary numbers ( $A_3$   $A_2$   $A_1$   $A_0$ ) and ( $B_3$   $B_2$   $B_1$   $B_0$ ), with  $A_0$  and  $B_0$  representing the LSB and  $A_3$  and  $B_3$  representing the MSB of the two numbers. The addition of these two numbers is performed as follows. We begin with the LSB position. We add the LSB bits and record the sum  $S_0$  below these bits in the same column and take the carry  $C_0$ , if any, to the next column of bits. For instance, if  $A_0 = 1$  and  $B_0 = 0$ , then  $S_0 = 1$  and  $C_0 = 0$ . Next, we add the bits  $A_1$  and  $B_1$  and the carry  $C_0$  from the previous addition. The process continues until we reach the MSB bits. The four steps are shown ahead.  $C_0$ ,  $C_1$ ,  $C_2$  and  $C_3$  are carry's, if any, produced as a result of adding first, second, third and fourth column bits respectively, starting from LSB and proceeding towards MSB. A similar procedure is followed when the given numbers have both integer as well as fractional parts:

#### **Addition Using the 2's Complement Method**

The 2's complement is the most commonly used code for processing positive and negative binary numbers. It forms the basis of arithmetic circuits in modern computers. When the decimal numbers to be added are expressed in 2's complement form, the addition of these numbers, following the basic laws of binary addition, gives correct results. Final carry obtained, if any, while adding MSBs should be disregarded. To illustrate this, we will consider the following four different cases:

- 1. Both the numbers are positive.

- 2. Larger of the two numbers is positive.

- 3. The larger of the two numbers is negative.

- 4. Both the numbers are negative.

#### Case 1

- Consider the decimal numbers +37 and +18.

- The 2's complement of +37 in eight-bit representation = 00100101.

- The 2's complement of +18 in eight-bit representation = 00010010.

- The addition of the two numbers, that is, +37 and +18, is performed as follows

00100101

+ 00010010

00110111

• The decimal equivalent of  $(00110111)_2$  is (+55), which is the correct answer.

#### Case 2

- Consider the two decimal numbers +37 and -18.

- The 2's complement representation of +37 in eight-bit representation = 00100101.

- The 2's complement representation of -18 in eight-bit representation = 11101110.

- The addition of the two numbers, that is, +37 and -18, is performed as follows:

00100101

+11101110

00010011

- The final carry has been disregarded.

- The decimal equivalent of  $(00010011)_2$  is +19, which is the correct answer.

#### Case 3

- Consider the two decimal numbers +18 and -37.

- -37 in 2's complement form in eight-bit representation = 11011011.

- +18 in 2's complement form in eight-bit representation = 00010010.

- The addition of the two numbers, that is, -37 and +18, is performed as follows:

11011011 + <u>00010010</u>

11101101

• The decimal equivalent of (11101101)<sub>2</sub>, which is in 2's complement form, is –19, which is the correct answer. 2's complement representation was discussed in detail in Chapter 1 on number systems.

#### Case 4

- Consider the two decimal numbers -18 and -37.

- -18 in 2's complement form is 11101110.

- -37 in 2's complement form is 11011011.

- The addition of the two numbers, that is, -37 and -18, is performed as follows

11011011

+11101110

11001001

- The final carry in the ninth bit position is disregarded.

- The decimal equivalent of (11001001)<sub>2</sub>, which is in 2's complement form, is -55, which is the correct answer.

It may also be mentioned here that, in general, 2's complement notation can be used to perform addition when the expected result of addition lies in the range from -2n-1 to +(2n-1-1), n being the number of bits used to represent the numbers. As an example, eight-bit 2's complement arithmetic cannot be used to perform addition if the result of addition lies outside the range from -128 to +127. Different steps to be followed to do addition in 2's complement arithmetic are summarized as follows:

- 1. Represent the two numbers to be added in 2's complement form.

- 2. Do the addition using basic rules of binary addition.

- 3. Disregard the final carry, if any.

- 4. The result of addition is in 2's complement form.

#### **Example**

Perform the following addition operations:

- 1.  $(275.75)_{10}$ +  $(37.875)_{10}$

- 2. (AF1.B3)<sub>16</sub>+ (FFF.E)<sub>16</sub>

#### Solution:1

1. As a first step, the two given decimal numbers will be converted into their equivalent binary numbers (decimal-to-binary conversion has been covered at length in Chapter 1, and therefore the decimal-to-binary conversion details will not be given here):

$$(275.75)_{10} = (100010011.11)_2$$

and  $(37.875)_{10} = (100101.111)_2$

The two binary numbers can be rewritten as  $(100010011.110)_2$  and  $(000100101.111)_2$  to have the same number of bits in their integer and fractional parts. The addition of two numbers is performed as follows:

100010011.110

000100101.111

100111001.101

The decimal equivalent of  $(100111001.101)_2$  is  $(313.625)_{10}$ .

01010111110001.10110011

01111111111111.11100000

1101011110001.10010011

The hexadecimal equivalent of (1101011110001.10010011)<sub>2</sub> is (1AF1.93)<sub>16</sub>, which is equal to the hex addition of (AF1.B3)<sub>16</sub> and (FFF.E)<sub>16</sub>.

#### Example:2

Find out whether 16-bit 2's complement arithmetic can be used to add 14 276 and 18 490.

#### **Solution**

The addition of decimal numbers 14 276 and 18 490 would yield 32 766. 16-bit 2's complement arithmetic has a range of -215 to +(215 - 1), i.e. -32 768 to +32 767. The expected result is inside the allowable range. Therefore, 16-bit arithmetic can be used to add the given numbers.

#### Example:3

Add –118 and –32 firstly using eight-bit 2's complement arithmetic and then using 16-bit 2's complement arithmetic. Comment on the results.

#### **Solution:**

- -118 in eight-bit 2's complement representation = 10001010.

- -32 in eight-bit 2's complement representation = 11100000.

- The addition of the two numbers, after disregarding the final carry in the ninth bit position, is 01101010. Now, the decimal equivalent of (01101010)<sub>2</sub>, which is in 2's complement form, is +106.

The reason for the wrong result is that the expected result, i.e. -150, lies outside the range of eight-bit 2's complement arithmetic. Eight-bit 2's complement arithmetic can be used when the expected result lies in the range from -27 to +(27-1), i.e. -128 to +127. -118 in 16-bit 2's complement representation = 11111111110001010.

- -32 in 16-bit 2's complement representation = 111111111111100000.

- The addition of the two numbers, after disregarding the final carry in the 17th position, produces 1111111101101010. The decimal equivalent of (1111111101101010)<sub>2</sub>, which is in 2's complement form, is -150, which is the correct answer. 16-bit 2's complement arithmetic has produced the correct result, as the expected result lies within the range of 16-bit 2's complement notation.

# **Subtraction of Larger-Bit Binary Numbers:**

Subtraction is also done column wise in the same way as in the case of the decimal number system. In the first step, we subtract the LSBs and subsequently proceed towards the MSB. Wherever the subtrahend (the bit to be subtracted) is larger than the minuend, we borrow from the next adjacent higher bit position having a '1'. As an example, let us go through different steps of subtracting (1001)<sub>2</sub> from (1100)<sub>2</sub>.

In this case, '1' is borrowed from the second MSB position, leaving a '0' in that position. The borrow is first brought to the third MSB position to make it '10'. Out of '10' in this position, '1' is taken to the LSB position to make '10' there, leaving a '1' in the third MSB position. 10 - 1 in the LSB column gives '1', 1 - 0 in the third MSB column gives '1', 0 - 0 in the second

MSB column gives '0' and 1-1 in the MSB also gives '0' to complete subtraction. Subtraction of mixed numbers is also done in the same manner. The above-mentioned steps are summarized as follows:

# **Subtraction Using 2's Complement Arithmetic:**

Subtraction is similar to addition. Adding 2's complement of the subtrahend to the minuend and disregarding the carry, if any, achieves subtraction. The process is illustrated by considering six different cases:

- 1. Both minuend and subtrahend are positive. The subtrahend is the smaller of the two.

- 2. Both minuend and subtrahend are positive. The subtrahend is the larger of the two.

- 3. The minuend is positive. The subtrahend is negative and smaller in magnitude.

- 4. The minuend is positive. The subtrahend is negative and greater in magnitude.

- 5. Both minuend and subtrahend are negative. The minuend is the smaller of the two.

- 6. Both minuend and subtrahend are negative. The minuend is the larger of the two.

#### Case 1

- Let us subtract +14 from +24.

- The 2's complement representation of +24 = 00011000.

- The 2's complement representation of +14 = 00001110.

- Now, the 2's complement of the subtrahend (i.e. +14) is 11110010.

- Therefore, +24 (+14) is given by

$$00011000 + 11110010 \over 00001010$$

with the final carry disregarded.

• The decimal equivalent of  $(00001010)_2$  is +10, which is the correct answer.

#### Case 2:

- Let us subtract +24 from +14.

- The 2's complement representation of +14 = 00001110.

- The 2's complement representation of +24 = 00011000.

- The 2's complement of the subtrahend (i.e. +24) = 11101000.

- Therefore, +14 (+24) is given by

00001110

+ <u>11101000</u>

11110110

• The decimal equivalent of  $(11110110)_2$ , which is of course in 2's complement form, is -10 which is the correct answer.

#### Case 3

- Let us subtract -14 from +24.

- The 2's complement representation of +24 = 00011000 = minuend.

- The 2's complement representation of -14 = 11110010 = subtrahend.

- The 2's complement of the subtrahend (i.e. -14) = 00001110.

- Therefore, +24 (-14) is performed as follows:

00011000

+00001110

00100110

• The decimal equivalent of  $(00100110)_2$  is +38, which is the correct answer.

#### Case 4

- Let us subtract -24 from +14.

- The 2's complement representation of +14 = 00001110 = minuend.

- The 2's complement representation of -24 = 11101000 = subtrahend.

- The 2's complement of the subtrahend (i.e. -24) = 00011000.

- Therefore, +14 (-24) is performed as follows:

00001110

+00011000

00100110

• The decimal equivalent of  $(00100110)_2$  is +38, which is the correct answer.

#### Case 5

- Let us subtract -14 from -24.

- The 2's complement representation of -24 = 11101000 = minuend.

The 2's complement representation of -14=11110010 = subtrahend.

- The 2's complement of the subtrahend = 00001110.

- Therefore, -24 (-14) is given as follows:

11101000

+00001110

11110110

• The decimal equivalent of (11110110)<sub>2</sub>, which is in 2's complement form, is -10, which is the correct answer.

#### Case 6

- Let us subtract -24 from -14.

- The 2's complement representation of -14 = 11110010 = minuend.

- The 2's complement representation of -24=11101000 = subtrahend.

- The 2's complement of the subtrahend = 00011000.

- Therefore, -14 (-24) is given as follows:

11110010

+00011000

#### 00001010

with the final carry disregarded.

The decimal equivalent of (00001010)<sub>2</sub>, which is in 2's complement form, is +10, which is the correct answer. It may be mentioned that, in 2's complement arithmetic, the answer is also in 2's complement notation, only with the MSB indicating the sign and the remaining bits indicating the magnitude. In 2's complement notation, positive magnitudes are represented in the same way as the straight binary numbers, while the negative magnitudes are represented as the 2's complement of their straight binary counterparts. A '0' in the MSB position indicates a positive sign, while a '1' in the MSB position indicates a negative sign. The different steps to be followed to do subtraction in 2's complement arithmetic are summarized as follows:

- 1. Represent the minuend and subtrahend in 2's complement form.

- 2. Find the 2's complement of the subtrahend.

- 3. Add the 2's complement of the subtrahend to the minuend.

- 4. Disregard the final carry, if any.

- 5. The result is in 2's complement form.

- 6. 2's complement notation can be used to perform subtraction when the expected result of subtraction lies in the range from -2n-1 to +(2n-1-1), n being the number of bits used to represent the numbers.

#### **Example**

Subtract (1110.011)<sub>2</sub> from (11011.11)<sub>2</sub> using basic rules of binary subtraction and verify the result by showing equivalent decimal subtraction.

#### **Solution:**

The minuend and subtrahend are first modified to have the same number of bits in the integer and fractional parts. The modified minuend and subtrahend are (11011.110)<sub>2</sub> and (01110.011)<sub>2</sub> respectively:

11011.110

-01110.011

#### 01101.011

The decimal equivalents of  $(11011.110)_2$  and  $(01110.011)_2$  are 27.75 and 14.375 respectively. Their difference is 13.375, which is the decimal equivalent of  $(01101.011)_2$ .

#### **Example**

Subtract (a)  $(-64)_{10}$  from  $(+32)_{10}$  and (b)  $(29.A)_{16}$  from  $(4F.B)_{16}$ . Use 2's complement arithmetic.

#### **Solution:**

(a)  $(+32)_{10}$  in 2's complement notation =  $(00100000)_2$ .

$(-64)_{10}$  in 2's complement notation =  $(11000000)_2$ .

The 2's complement of  $(-64)_{10} = (01000000)_2$ .

$(+32)_{10} - (-64)_{10}$  is determined by adding the 2's complement of  $(-64)_{10}$  to  $(+32)_{10}$ .

Therefore, the addition of  $(00100000)_2$  to  $(01000000)_2$  should give the result. The operation is shown as follows:

00100000

+01000000

01100000

The decimal equivalent of  $(01100000)_2$  is +96, which is the correct answer as +32 - (-64) = +96.

(b) The minuend =  $(4F.B)_{16} = (01001111.1011)_2$ .

The minuend in 2's complement notation =  $(01001111.1011)_2$ .

The subtrahend =  $(29.A)_{16} = (00101001.1010)_2$ .

The subtrahend in 2's complement notation =  $(00101001.1010)_2$ .

The 2's complement of the subtrahend =  $(11010110.0110)_2$ .

$(4F.B)_{16} - (29.A)_{16}$  is given by the addition of the 2's complement of the subtrahend to the minuend.

01001111.1011

+ <u>11010110.0110</u>

00100110.0001

with the final carry disregarded. The result is also in 2's complement form. Since the result is a positive number, 2's complement notation is the same as it would be in the case of the straight binary code. The hex equivalent of the resulting binary number =  $(26.1)_{16}$ , which is the correct answer.

#### **BCD** Addition and Subtraction in Excess-3 Code:

Below, we will see how the excess-3 code can be used to perform addition and subtraction operations on BCD numbers.

#### Addition:

The excess-3 code can be very effectively used to perform the addition of BCD numbers. The steps to be followed for excess-3 addition of BCD numbers are as follows:

- 1. The given BCD numbers are written in excess-3 form by adding '0011' to each of the four-bit groups.

- 2. The two numbers are then added using the basic laws of binary addition.

- 3. Add '0011' to all those four-bit groups that produce a carry, and subtract '0011' from all those four-bit groups that do not produce a carry during addition.

- 4. The result thus obtained is in excess-3 form.

#### **Subtraction:**

Subtraction of BCD numbers using the excess-3 code is similar to the addition process discussed above. The steps to be followed for excess-3 subtraction of BCD numbers are as follows:

- 1. Express both minuend and subtrahend in excess-3 code.

- 2. Perform subtraction following the basic laws of binary subtraction.

- 3. Subtract '0011' from each invalid BCD four-bit group in the answer.

- 4. Subtract '0011' from each BCD four-bit group in the answer if the subtraction operation of the relevant four-bit groups required a borrow from the next higher adjacent four-bit group.

- 5. Add '0011' to the remaining four-bit groups, if any, in the result.

- 6. This gives the result in excess-3 code.

The process of addition and subtraction can be best illustrated with the help of following examples.

#### **Example:**

Add  $(0011\ 0101\ 0110)_{BCD}$  and  $(0101\ 0111\ 1001)_{BCD}$  using the excess-3 addition method and verify the result using equivalent decimal addition.

#### **Solution**

The excess-3 equivalents of 0011 0101 0110 and 0101 0111 1001 are 0110 1000 1001 and 1000 1010 1100 respectively. The addition of the two excess-3 numbers is given as follows:

0110 1000 1001

1000 1010 1100

<u>1111 0011 0101</u>

After adding 0011 to the groups that produced a carry and subtracting 0011 from the groups that did not produce a carry, we obtain the result of the above addition as 1100 0110 1000. Therefore, 1100 0110 1000 represents the excess-3 code for the true result. The result in BCD code is 1001 0011 0101, which is the BCD equivalent of 935. This is the correct answer as the addition of the given BCD numbers 0011 0101 0110 =  $(356)_{10}$  and 0101 0111  $1001 = (579)_{10}$  yields  $(935)_{10}$  only.

#### **Example:**

Perform  $(185)_{10}$ – $(8)_{10}$  using the excess-3 code.

#### **Solution:**

- $(185)_{10} = (0001\ 1000\ 0101)_{BCD}$ . The excess-3 equivalent of  $(0001\ 1000\ 0101)_{BCD} = 0100\ 1011$  1000.

- $(8)_{10} = (008)_{10} = (0000\ 0000\ 1000)\ _{BCD}$ . The excess-3 equivalent of (0000 0000 1000)  $_{BCD} = 0011\ 0011\ 1011$ .

- Subtraction is performed as follows:

0100 1011 1000

- 0011 0011 1011

#### 0001 0111 1101

- In the subtraction operation, the least significant column of four-bit groups needed a borrow, while the other two columns did not need any borrow. Also, the least significant column has produced an invalid BCD code group. Subtracting 0011 from the result of this column and adding 0011 to the results of other two columns, we get 0100 1010 1010. This now constitutes the result of subtraction expressed in excess-3 code.

- The result in BCD code is therefore 0001 0111 0111.

- The decimal equivalent of 0001 0111 0111 is 177, which is the correct result.

#### 1.4. Boolean laws:

The laws of Boolean algebra can be used to simplify many a complex Boolean expression and also to transform the given expression into a more useful and meaningful equivalent expression.

These are the rules we use to simplify logical expressions and design efficient circuits.

#### 1. Identity Law:

In the Boolean Algebra, we have identity elements for both AND(.) and OR (+) operations. The identity law states that in Boolean algebra, we have such variables that, on operating with the AND and OR operations we get the same result, i.e.

- A + 0 = A

- $\bullet \quad A.1 = A$

#### 2. Commutative Law:

Binary variables in Boolean Algebra follow the commutative law. This law states that operating Boolean variables A and B is similar to operating Boolean variables B and A. That is,

- A. B = B. A

- $\bullet \quad A+B=B+A$

#### 3. Associative Law:

Associative law states that the order of performing Boolean operator is illogical as their result is always the same. This can be understood as,

- (A . B) . C = A . (B . C)

- (A + B) + C = A + (B + C)

# 4. Distributive Law:

Boolean Variables also follow the distributive law, and the expression for the Distributive law is given as:

•

$$A \cdot (B + C) = (A \cdot B) + (A \cdot C)$$

#### 5. Inversion Law:

Inversion law is the unique law of Boolean algebra that states, the complement of the complement of any number is the number itself.

•

$$(A')' = A$$

Apart from these other laws are mentioned below:

#### 6. AND Law:

AND law of the Boolean algebra uses AND operator and the AND law is,

- $A \cdot 0 = 0$

- $A \cdot 1 = A$

- $\bullet$   $A \cdot A = A$

#### 7. OR Law:

OR law of the Boolean algebra uses OR operator and the OR law is,

- A + 0 = A

- A + 1 = 1

- $\bullet \quad A + A = A$

# 8. Complement Law:

The Complement Law states that a variable ORed with its complement is always 1, and a variable ANDed with its complement is always 0.

- A + A' = 1

- $A \cdot A' = 0$

#### 9. Domination Law:

The **Domination Law** states that any variable ORed with 1 will always be 1, and any variable ANDed with 0 will always be 0.

- A + 1 = 1

- $A \cdot 0 = 0$

# 10. Double Negation Law:

The **Double Negation Law** states that the complement of the complement of a variable is the variable itself.

•

$$(A')' = A$$

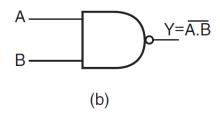

# 1.6.DeMorgan's Theorem:

De Morgan's Theorem is a powerful theorem in Boolean algebra which has a set of two rules or laws. These two laws were developed to show the relationship between two variable AND, OR, and NOT operations. These two rules enable the variables to be negated, i.e. opposite of their original form. Therefore, DeMorgan's theorem gives the dual of a logic function.

Now, let us discuss the two laws of De Morgan's theorem.

# De Morgan's First Theorem (Law 1):

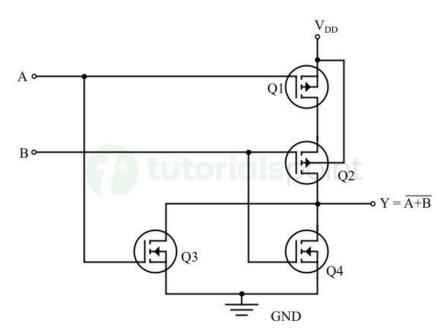

De Morgan's First Law states that the complement of a sum (ORing) of variables is equal to the product (ANDing) of their individual complements. In other words, the complement of two or more ORed variables is equivalent to the AND of the complements of each of the individual variables, i.e.

$$\overline{A} + \overline{B} = \overline{A} \cdot \overline{B}$$

Or, it may also be represented as,

$$(A+B)'=A'\cdot B'$$

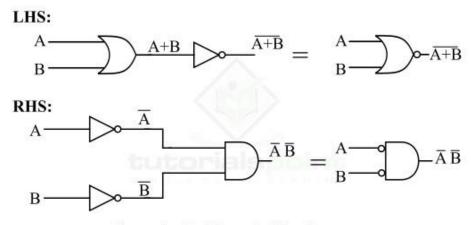

The logic implementation of left side and right side of this law is shown in Figure.

Figure 1 - De Morgan's First Law

Thus, DeMorgan's first law proves that the NOR gate is equivalent to a bubbled AND gate. The following truth table shows the proof of this law.

|     | Left Side |          |     | Righ | at Side |

|-----|-----------|----------|-----|------|---------|

| Inp | out       | Output   | Inp | out  | Output  |

| A   | В         | (A + B)' | A'  | В'   | A'· B'  |

| 0   | 0         | 1        | 1   | 1    | 1       |

| О   | 1         | 0        | 1   | 0    | 0       |

| 1   | 0         | 0        | 0   | 1    | 0       |

| 1   | 1         | 0        | 0   | 0    | 0       |

This truth table proves that the Boolean expression on the left is equivalent to that on the right side of the expression of De Morgan's first law.

Also, the first law of De Morgan's theorem can be extended to any number of variables, or a combination of variables.

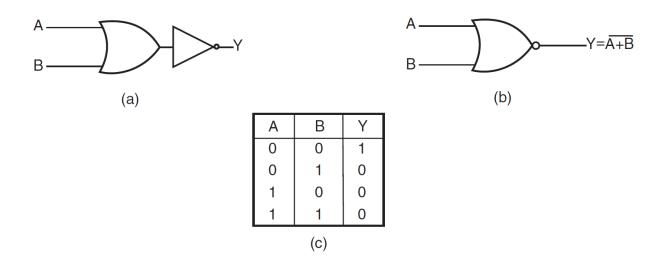

# De Morgan's Second Theorem (Law 2)

De Morgan's second law states that the complement of the product (ANDing) of variables is equivalent to the sum (ORing) of their individual complements.

In other words, the complement of two or more ANDed variables is equal to the sum of the complement of each of the individual variables, i.e.,

$$\overline{A.B} = \overline{A} + \overline{B}$$

It may also be represented as,

$$(AB)'=A'+B'$$

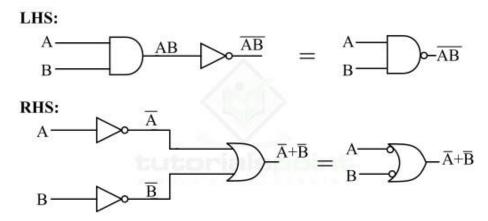

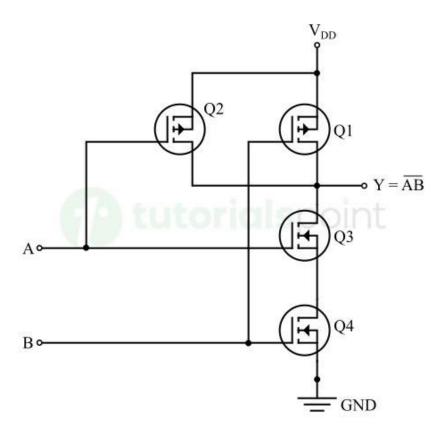

The logic implementation of left and right sides of this expression is shown in Figure 2.

Figure 2 - De Morgan's Second Law

Hence, De Morgan's second law proves that the NAND gate is equivalent to a bubbled OR gate. The following truth table shows the proof of this law.

| Left Side |   | Right Side |       |    |         |

|-----------|---|------------|-------|----|---------|

| Input     |   | Output     | Input |    | Output  |

| A         | В | AB         | A'    | B' | A' + B' |

| 0 | 0 | 0 | 1 | 1 | 1 |

|---|---|---|---|---|---|

| 0 | 1 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 | 0 |

This truth table proves that the Boolean expression on the left side is equivalent to that on the right side of the expression of De Morgan's second law.

Similar to the first law, we may extend the De Morgan's second law for any number of variables or combination of variables.

# 1.7. Basic logic gates:

The logic gate is the most basic building block of any digital system, including computers. Each one of the basic logic gates is a piece of hardware or an electronic circuit that can be used to implement some basic logic expression. While laws of Boolean algebra could be used to do manipulation with binary variables and simplify logic expressions, these are actually implemented in a digital system with the help of electronic circuits called logic gates. The three basic logic gates are the OR gate, the AND gate and the NOT gate.

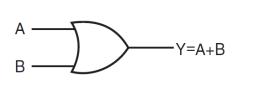

#### **OR Gate:**

An OR gate performs an ORing operation on two or more than two logic variables. The OR operation on two independent logic variables A and B is written as Y = A+B and reads as Y equals A OR B and not as A plus B. An OR gate is a logic circuit with two or more inputs and one output. The output of an OR gate is LOW only when all of its inputs are LOW. For all other possible input combinations, the output is HIGH. This statement when interpreted for a positive logic system means the following. The output of an OR gate is a logic '0' only when all of its inputs are at logic '0'. For all other possible input combinations, the output is a logic '1'. Figure

shows the circuit symbol and the truth table of a two-input OR gate. The operation of a two-input OR gate is explained by the logic expression

$$Y = A + B$$

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

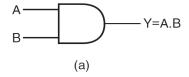

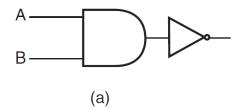

#### **AND Gate:**

An AND gate is a logic circuit having two or more inputs and one output. The output of an AND gate is HIGH only when all of its inputs are in the HIGH state. In all other cases, the output is LOW. When interpreted for a positive logic system, this means that the output of the AND gate is a logic '1' only when all of its inputs are in logic '1' state. In all other cases, the output is logic '0'. The logic symbol and truth table of a two-input AND gate are shown in Figs (a) and (b) respectively. The AND operation on two independent logic variables A and B is written as Y = A.B and reads as Y equals A AND B and not as A multiplied by B. Here, A and B are input logic variables and Y is the output. An AND gate performs an ANDing operation:

| Α   | В | Υ      |  |  |

|-----|---|--------|--|--|

| 0   | 0 | 0      |  |  |

| 0   | 1 | 0<br>0 |  |  |

| 1   | 0 | 0      |  |  |

| 1   | 1 | 1      |  |  |

| (b) |   |        |  |  |

Digital Electronics And Microprocessor 8085

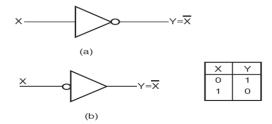

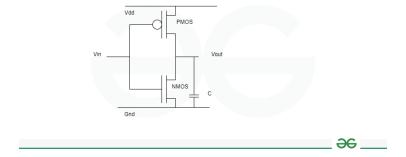

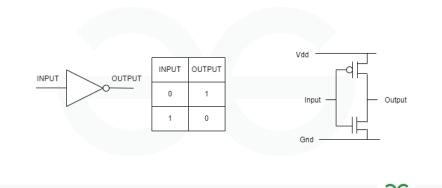

# **NOT Gate:**

A NOT gate is a one-input, one-output logic circuit whose output is always the complement of the input. That is, a LOW input produces a HIGH output, and vice versa. When interpreted for a positive logic system, a logic '0' at the input produces a logic '1' at the output, and vice versa. It is also known as a 'complementing circuit' or an 'inverting circuit'. Figure shows the circuit symbol and the truth table. The NOT operation on a logic variable X is denoted as  $\overline{X}$  or X'. That is, if X is the input to a NOT circuit, then its output Y is given by  $Y = \overline{X}$  or X' and reads as Y equals NOT X. Thus, if X = 0, Y = 1 and if X = 1, Y = 0.

# 1.7. Universal logic gates (NAND & NOR):

#### **NAND Gate:**

NAND stands for NOT AND. An AND gate followed by a NOT circuit makes it a NAND gate. Figure shows the circuit symbol of a two-input NAND gate. The truth table of a NAND gate is obtained from the truth table of an AND gate by complementing the output entries. The output of a NAND gate is a logic '0' when all its inputs are a logic '1'. For all other input combinations, the output is a logic '1'. NAND gate operation is logically expressed as

$$Y = \overline{A \cdot B}$$

In general, the Boolean expression for a NAND gate with more than two inputs can be written as

$$Y = \overline{(A, B. C. D...)}$$

| Α | В   | Υ |

|---|-----|---|

| 0 | 0   | 1 |

| 0 | 1   | 1 |

| 1 | 0   | 1 |

| 1 | 1   | 0 |

|   | (c) |   |

### **NOR Gate:**

NOR stands for NOT OR. An OR gate followed by a NOT circuit makes it a NOR gate. The truth table of a NOR gate is obtained from the truth table of an OR gate by complementing the output entries. The output of a NOR gate is a logic ' 1 ' when all its inputs are logic ' 0 '. For all other input combinations, the output is a logic ' 0 '. The output of a two-input NOR gate is logically expressed as

$$Y = \overline{(A+B)}$$

In general, the Boolean expression for a NOR gate with more than two inputs can be written as

$$Y = \overline{(A + B + C + D \dots)}$$

# 1.8. standard representation of logic functions (SOP & POS):

SOP and POS are two of the important topics of the Boolean algebra. SOP refers to the sum of the product of the minterms, whereas POS is the Product of the sum of terms. SOP and POS help us simplify the complex Boolean variables and are mainly used in K-maps.

#### What is SOP?

The SOP stands for Sum of Products defined as the sum of minterms. As the name suggests the SOP form represents the OR operation of the product terms i.e., minterms. The SOP represents the minterms in the Boolean algebra. The SOP is denoted by  $\Sigma$ . As the SOP deals with the minterms it works on active high logic.

#### **Example of SOP**

- AB + CD

- P'Q + R

- X'Y' + W'Z'

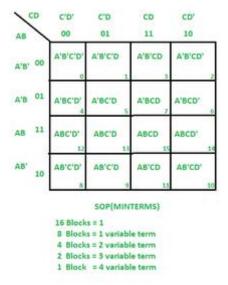

#### **SOP** in K-Map

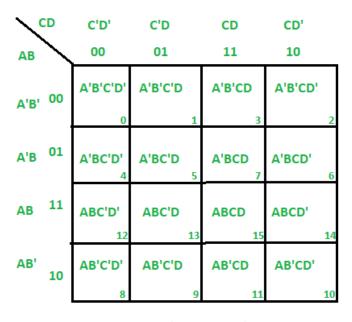

The below image represents the SOP in K-map.

SOP(MINTERMS)

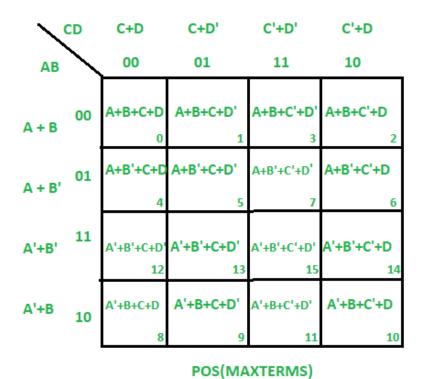

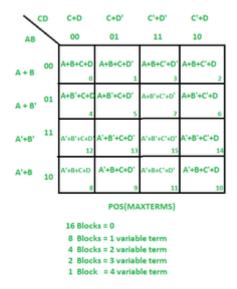

#### What is POS?

The POS stands for Product of Sum defined as the product of maxterms. As the name suggests the POS form represents the AND operation of the sum terms i.e., maxterms. The POS represents the maxterms in Boolean algebra. The POS is denoted by  $\Pi$ . As the POS deals with the maxterms it works on active low logic.

#### **Example of POS**

- $\bullet \quad (A+B).(C+D)$

- (P' + Q).(R + S')

#### POS in K-Map

Below image represents the POS in K-map.

**SOP vs POS**

| Characterization | SOP                            | POS                             |  |  |

|------------------|--------------------------------|---------------------------------|--|--|

| Definition       | SOP is sum of the minterms.    | POS is the product of maxterms. |  |  |

| Stands for       | SOP stands for Sum of Product. | POS stands for Product of Sum.  |  |  |

| Representation   | It represents minterms.        | It represents maxterms.         |  |  |

| Characterization | SOP                            | POS                           |  |

|------------------|--------------------------------|-------------------------------|--|

| Logic            | It works on active high logic. | It works on active low logic. |  |

| Denotation       | It is denoted by $\Sigma$ .    | It is denoted by Π.           |  |

| Output           | The output of SOP is 1.        | The output of POS is 0.       |  |

# 1.9. Minimization techniques (Karnaugh map: 2, 3, 4 variables):

### Karnaugh Map Method:

In many digital circuits and practical problems, we need to find expressions with minimum variables. We can minimize Boolean expressions of 3, 4 variables very easily using K-map without using any Boolean algebra theorems. It is a tool which is used in digital logic to simplify boolean expression. It helps to simplify logic into simpler form by organizing grid from truth table values. This helps it to create a minimal Boolean expressions by identifying patterns.

#### K-map can take two forms:

- 1. Sum of product (SOP)

- 2. Product of Sum (POS)

According to the need of problem. K-map is a table-like representation, but it gives more information than the TABLE. We fill a grid of the K-map with 0's and 1's then solve it by making groups.

# Steps to Solve Expression using K-map:

- 1. Select the K-map according to the number of variables.

- 2. Identify minterms or maxterms as given in the problem.

- 3. For SOP put 1's in blocks of K-map respective to the minterms (0's elsewhere).

- 4. For POS put 0's in blocks of K-map respective to the max terms (1's elsewhere).

- 5. Make rectangular groups containing total terms in power of two like 2,4,8 ..(except 1) and try to cover as many elements as you can in one group.

- 6. From the groups made in step 5 find the product terms and sum them up for SOP form.

## **SOP FORM (Sum of Product Form):**

SOP form is way to simplify and write Boolean expressions using AND to combine inputs and OP to combine the results.

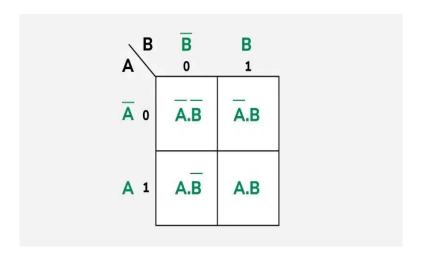

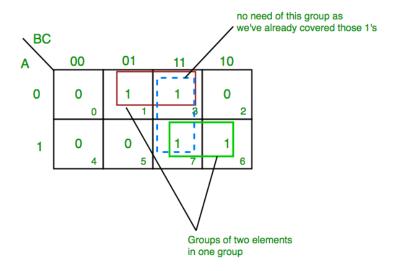

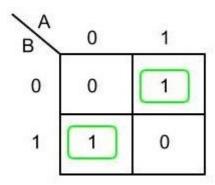

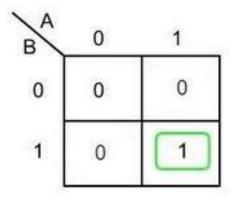

# 1. K-map for 2 variables:

In the 2 variable k-map, four squares are constructed. Each square contains one term of expression with two variables.

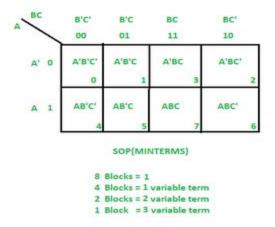

# 2. K-map of 3 variables

# $Z = \Sigma A, B, C(1,3,6,7)$

From red group we get product term:

A'C

From green group we get product term:

AB

Summing these product terms we get-Final expression (A'C+AB)

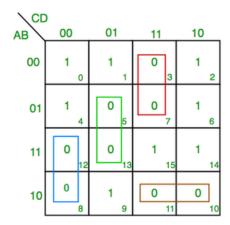

## 3. K-map for 4 variables

$F(A,B,C,D)=\Sigma(0,1,2,3,12,13,15,14)$

| \ c | D  |    |    |    |

|-----|----|----|----|----|

| AB  | 00 | 01 | 11 | 10 |

| 00  | 1  | 1  | 1  | 1  |

| 01  | 0  | 0  | 0  | 0  |

| 11  | 1  | 1  | 1  | 1  |

| 10  | 0  | 0  | 0  | 0  |

|     |    |    |    |    |

From red group we get product term:

AB

From green group we get product term:

A'B'

Summing these product terms we get-Final expression (AB+A'B').

# **POS FORM (Product of Sum Form):**

POS form is a way to simplify and write Boolean expressions using OR to combine terms inside parentheses and then AND to combine those groups.

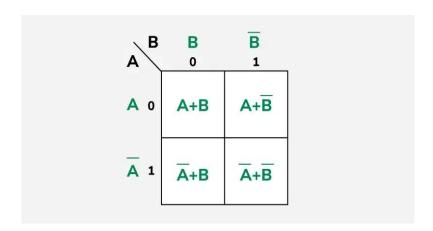

#### 1.K-map of 2 variables

In the 2 variable k-map, four squares are constructed. Each square contains one term of expression with two variables.

# 2. K-map of 3 variables:

K-map 3 variable POS form

.

Digital Electronics And Microprocessor 8085

$F(A,B,C)=\Sigma(0,3,6,7)$

| $\setminus$ | BC <sub>oo</sub> | 01 | 11  | 10  |

|-------------|------------------|----|-----|-----|

| <b>A</b> °  | 0 。              | 1  | 0 3 | 1 2 |

| 1           | 1                | 1  | 0   | 0   |

|             | 4                | 5  | 7   | 6   |

From red group we find terms

A B

Taking complement of these two

A' B'

Now sum up them

(A' + B')

From brown group we find terms

B C

Taking complement of these two terms

В' С'

Now sum up them

(B'+C')

From yellow group we find terms

A' B' C'

Taking complement of these two

A B C

Now sum up them

$$(A + B + C)$$

We will take product of these three terms: Final expression -

$$(A' + B')(B' + C')(A + B + C)$$

# 3. K-map of 4 variables:

# K-map 4 variable POS form

$F(A,B,C,D)=\Sigma(3,5,7,8,10,11,12,13)$

Digital Electronics And Microprocessor 8085

From green group we find terms

C' D B

Taking their complement and summing them

(C+D'+B')

From red group we find terms

C D A'

Taking their complement and summing them

(C'+D'+A)

From blue group we find terms

A C' D'

Taking their complement and summing them

(A'+C+D)

From brown group we find terms

AB'C

Taking their complement and summing them

(A'+B+C')

Finally we express these as product -

(C+D'+B').(C'+D'+A).(A'+C+D).(A'+B+C')

## **Advantages of K-MAP:**

- Makes Logic Simpler: It makes complicated Boolean expressions simpler.

- Minimizes Logic Gates: Simplifying the logic helps us to use fewer logic gates, making circuits more efficient.

- Reduce Errors: The visual representation of k-map helps to avoid errors while simplifying.

- Time-Saving: It's quicker than traditional methods for simplifying logic.

• No need for Boolean Laws: K-map doesn't require deep knowledge of Boolean laws, making it easy for beginners.

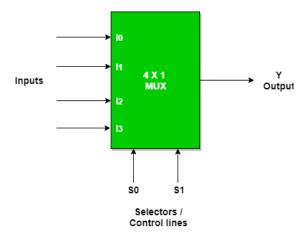

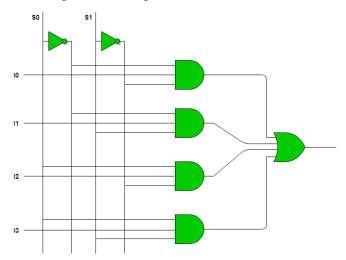

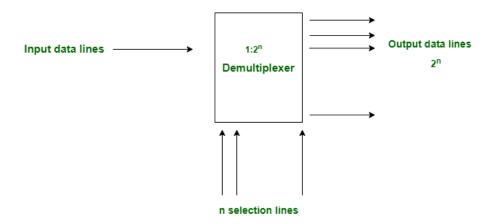

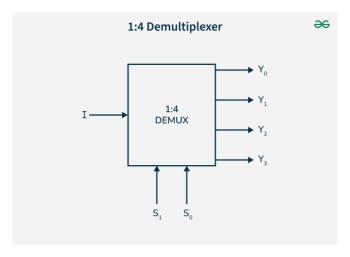

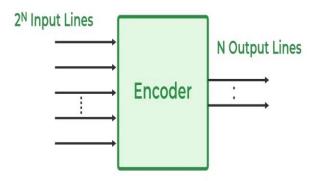

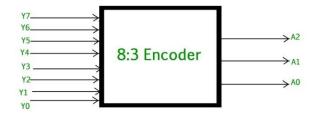

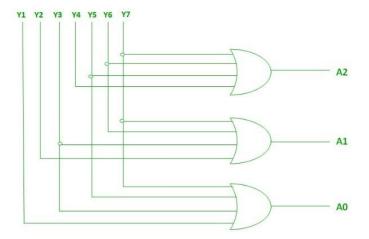

**UNIT-II: ADDERS**: half & full adder – subtractors: half & full subtractor – parallel binary adder – magnitude comparator – multiplexers (4:1) & demultiplexers (1:4), encoder (8-line to 3-line) and decoder (3-line to 8-line), BCD to seven segment decoders.

## 2.1. Half & full adder:

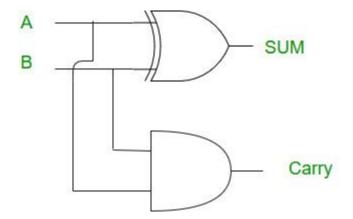

#### Half adder:

A half adder is a basic combinational circuit that adds two single-bit binary inputs (A and B) to produce a SUM using an XOR gate and a CARRY using an AND gate, without considering any carry-in from a previous stage.

- Performs binary addition of two 1-bit inputs, generating a SUM (A ⊕ B) and CARRY (A

· B).

- Cannot handle carry-in from a previous stage, making it suitable only for the first stage of multi-bit addition.

The Boolean expressions for the SUM and CARRY outputs are given by the equations

- SUM  $S = A.\overline{B} + .\overline{A}.B$

- CARRYC = A.B

#### **Truth Table of Half Adder:**

Below is the truth table, illustrating the operation of a half adder

| A | В | Sum | Carry |

|---|---|-----|-------|

| 0 | 0 | 0   | 0     |

| 0 | 1 | 1   | 0     |

| 1 | 0 | 1   | 0     |

| 1 | 1 | 0   | 1     |

# **Logical Expression of Half Adder**

Here we perform two operations Sum and Carry, thus we need two K-maps one for each to derive the expression.

For

Sum = A XOR B

For

Carry = A AND B

# Implementation of Half Adder:

Half adder has only two inputs and there is no provision to add a carry coming from the lower order bits when multi addition is performed.

### **Advantages of Half Adder in Digital Logic**

- **Simplicity:** A half adder is a straightforward circuit that requires a couple of fundamental parts like XOR AND entryways. It is not difficult to carry out and can be utilized in numerous advanced frameworks.

- **Speed:** The half adder works at an extremely rapid, making it reasonable for use in fast computerized circuits.

### **Application of Half Adder in Digital Logic:**

- Arithmetic circuits: Half adders are utilized in number-crunching circuits to add double numbers. At the point when different half adders are associated in a chain, they can add multi-bit double numbers.

- **Data handling:** Half adders are utilized in information handling applications like computerized signal handling, information encryption, and blunder adjustment.

- Address unravelling: In memory tending to, half adders are utilized in address deciphering circuits to produce the location of a particular memory area.

- Encoder and decoder circuits: Half adders are utilized in encoder and decoder circuits for computerized correspondence frameworks.

- **Multiplexers and demultiplexers:** Half adders are utilized in multiplexers and demultiplexers to choose and course information.

- Counters: Half adders are utilized in counters to augment the count by one.

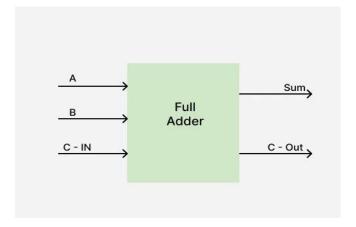

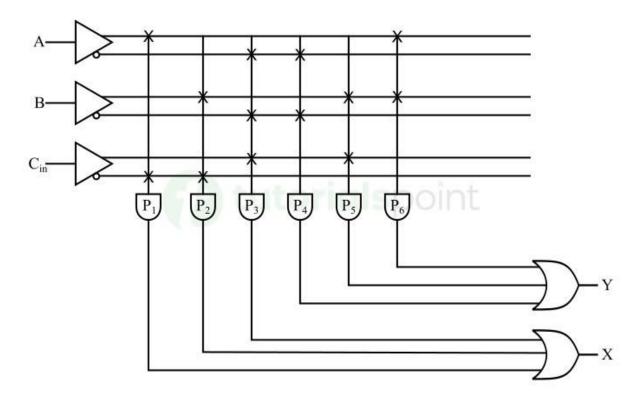

# **Full Adder:**

Full Adder is a combinational circuit that adds three inputs and produces two outputs. The first two inputs are A and B and the third input is an input carry as C-IN. The output carry is designated as C-OUT and the normal output is designated as S which is SUM.

- The C-OUT is also known as the majority 1's detector, whose output goes high when more than one input is high.

- A full adder logic is designed in such a manner that can take eight inputs together to create a byte-wide adder and cascade the carry bit from one adder to another.

- We use a full adder because when a carry-in bit is available, another 1-bit adder must be used since a 1-bit half-adder does not take a carry-in bit.

- A 1-bit full adder adds three operands and generates 2-bit results.

#### **Full Adder Truth Table**

A Full Adder takes three binary inputs:

- A (first bit)

- B (second bit)

- C-IN (carry input)

And it produces two outputs:

- Sum (S)

- Carry Out (C-OUT)

Digital Electronics And Microprocessor 8085

Here's the truth table for the full adder:

| INI | PUT |      | OUTPUT |       |  |

|-----|-----|------|--------|-------|--|

| A   | В   | C-IN | Sum    | C-OUT |  |

| 0   | 0   | 0    | 0      | 0     |  |

| О   | 0   | 1    | 1      | 0     |  |

| О   | 1   | 0    | 1      | 0     |  |

| 0   | 1   | 1    | 0      | 1     |  |

| 1   | 0   | 0    | 1      | 0     |  |

| 1   | О   | 1    | 0      | 1     |  |

| 1   | 1   | 0    | 0      | 1     |  |

| 1   | 1   | 1    | 1      | 1     |  |

## **Logical Expressions for SUM**

From the truth table, the logical expression for the sum (S) in a full adder is:

$$S = A'B'C\text{-}IN + A'BC\text{-}IN' + AB'C\text{-}IN' + ABC\text{-}IN$$

Since  $A'B + AB' = A \oplus B$ . This simplifies to:

$$S = C-IN(A \oplus B)' + C-IN'(A \oplus B)$$

The final simplified expression is:

#### $S = A \oplus B \oplus C-IN$

Thus, the sum output is the XOR of A, B, and C-IN.

#### **Logical Expression for C-OUT**

From the truth table, the logical expression for **C-OUT** (carry-out) in a full adder is:

$$C$$

- $OUT = A'BC$ - $IN + AB'C$ - $IN + ABC$ - $IN' + ABC$ - $IN'$

This simplifies to:

$$C$$

- $OUT = A B(C$ - $IN'$ + $C$ - $IN) + C$ - $IN(A'B$ + $AB')$

Since C-IN' + C-IN = 1 and A'B + AB' = A  $\bigoplus$  B. Thus, the final simplified expression is:

$$C$$

- $OUT = A B + C$ - $IN (A  $\bigoplus B)$$

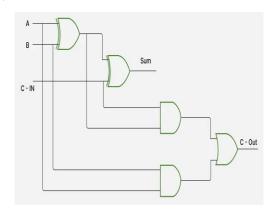

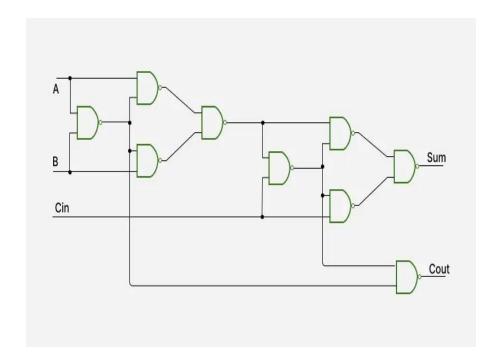

#### Logic Circuit of Full Adder

To implement a Full Adder using basic logic gates:

#### Sum (S) is implemented using XOR gates:

Use two XOR gates:

- First XOR gate:  $A \oplus B$

- Second XOR gate:  $(A \oplus B) \oplus C$ -IN to get the final sum S.

Carry (C-Out) is implemented using XOR, AND and OR gates: Finally, the two outputs from the AND gates are combined using an OR gate to generate the final C-OUT output.

First AND gate: This gate calculates A AND B.

**Second AND gate**: This gate calculates C-IN AND (A  $\oplus$  B). To do this, you need the result of the first XOR gate (A  $\oplus$  B) as an input to the second AND gate.

Digital Electronics And Microprocessor 8085

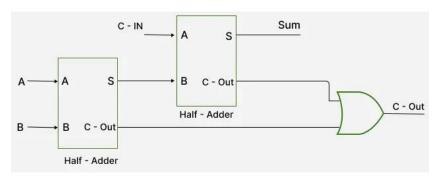

# Implementation of Full Adder using Half Adders

2 Half Adders and an OR gate is required to implement a Full Adder.

With this logic circuit, two bits can be added together, taking a carry from the next lower order of magnitude, and sending a carry to the next higher order of magnitude.

# Implementation of Full Adder using NAND gates

Total 9 NAND gates are required to implement a Full Adder.

# Implementation of Full Adder using NOR gates

Total 9 NOR gates are required to implement a Full Adder.

# **Application of Full Adder in Digital Logic**

- **Arithmetic circuits:** Full adders are utilized in math circuits to add twofold numbers. At the point when different full adders are associated in a chain, they can add multi-bit paired numbers.

- **Data handling:** Full adders are utilized in information handling applications like advanced signal handling, information encryption, and mistake rectification.

- Counters: Full adders are utilized in counters to addition or decrement the count by one.

- **Multiplexers and demultiplexers:** Full adders are utilized in multiplexers and demultiplexers to choose and course information.

- **Memory tending to:** Full adders are utilized in memory addressing circuits to produce the location of a particular memory area.

- **ALUs:** Full adders are a fundamental part of Number juggling Rationale Units (ALUs) utilized in chip and computerized signal processors.

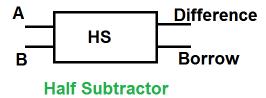

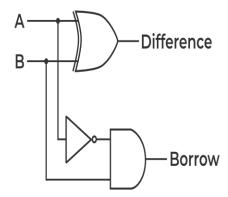

## 2.2. Half-Subtractor:

A half subtractor is a digital logic circuit that performs the binary subtraction of two single-bit binary numbers. It has two inputs, A and B, and two outputs, Difference and Borrow. The Difference output represents the result of subtracting B from A, while the Borrow output indicates whether a borrow is needed when A is smaller than B. The half subtractor can be implemented using basic logic gates such as XOR, AND, and NOT gates. It is a fundamental building block for more complex arithmetic circuits like full subtractors and multi-bit subtractors.

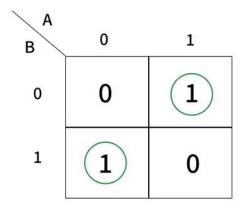

**Truth Table of Half Subtractor**

| Α | В | Diff | Borrow |

|---|---|------|--------|

| 0 | 0 | 0    | 0      |

| 0 | 1 | 1    | 1      |

| 1 | 0 | 1    | 0      |

| 1 | 1 | 0    | 0      |

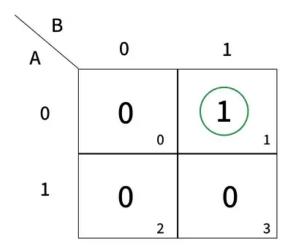

# **Logical Expression of Half Subtractor**

For difference,

The SOP form of the Difference is as follows:

Difference = A'B+AB'

For borrow,

The SOP form of the Borrow is as follows:

Borrow = A'B

## **Implementation of Half Subtractor:**

#### **Application of Half Subtractor in Digital Logic:**

- Calculators: Most mini-computers utilize advanced rationale circuits to perform numerical tasks. A Half Subtractor can be utilized in a number cruncher to deduct two parallel digits from one another.

- Alarm Systems: Many caution frameworks utilize computerized rationale circuits to identify and answer interlopers. A Half Subtractor can be utilized in these frameworks to look at the upsides of two parallel pieces and trigger a caution in the event that they are unique.

- Automotive Systems: Numerous advanced vehicles utilize computerized rationale circuits

to control different capabilities, like the motor administration framework, stopping

mechanism, and theatre setup. A Half Subtractor can be utilized in these frameworks to

perform computations and examinations.

- Security Frameworks: Advanced rationale circuits are usually utilized in security frameworks to identify and answer dangers. A Half Subtractor can be utilized in these frameworks to look at two double qualities and trigger a caution in the event that they are unique.

• Computer Frameworks: Advanced rationale circuits are utilized broadly in PC frameworks to perform estimations and examinations. A Half Subtractor can be utilized in a PC framework to deduct two paired values from one another.

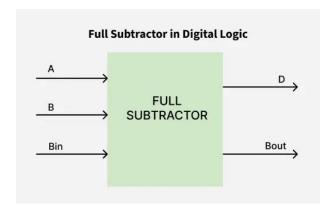

#### **Full Subtractor:**

A Full Subtractor is a combinational circuit used to perform binary subtraction. It has three inputs:

- A (Minuend)

- B (Subtrahend)

- B-IN (Borrow-in from the previous stage)

#### It produces two outputs:

- Difference (D): The result of the subtraction.

- Borrow-out (B-OUT): Indicates if a borrow is needed for the next stage.

The full subtractor is essential because a half-subtractor can only subtract the least significant bit (LSB) of binary numbers. However, if a borrow is generated during the subtraction of the LSBs, it will affect the subtraction in the next stages. A full subtractor handles this situation by considering the borrow from the previous stage, ensuring accurate subtraction even when a borrow is present.

The full subtractor is used to subtract binary numbers with borrow handling, making it suitable for multi-bit subtraction in digital circuits like Arithmetic Logic Units (ALUs).

Digital Electronics And Microprocessor 8085

# **Truth Table of Full Subtractor**

| Inp | out |     | Output |      |  |

|-----|-----|-----|--------|------|--|

| A   | В   | Bin | D      | Bout |  |

| О   | О   | O   | 0      | 0    |  |

| О   | О   | 1   | 1      | 1    |  |

| О   | 1   | О   | 1      | 1    |  |

| О   | 1   | 1   | 0      | 1    |  |

| 1   | О   | О   | 1      | 0    |  |

| 1   | О   | 1   | 0      | 0    |  |

| 1   | 1   | О   | 0      | 0    |  |

| 1   | 1   | 1   | 1      | 1    |  |

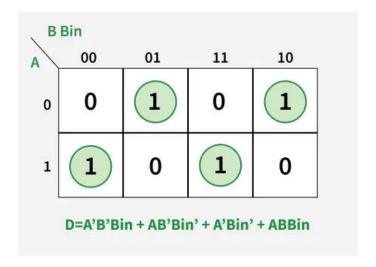

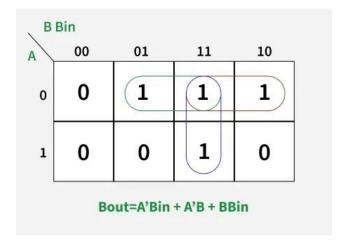

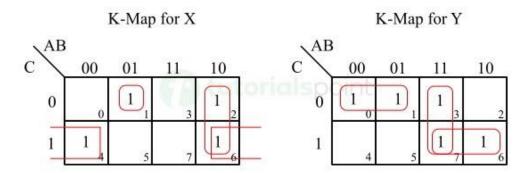

# K-Map for Full Subtractor:

From above table we can draw the K-Map as shown for "difference" and "borrow".

# Logical expression for difference

The basic expression is:

$$D = A'B'Bin + A'BBin' + AB'Bin' + ABBin$$

Factoring common terms:

$$D = Bin(A'B' + AB) + Bin'(AB' + A'B)$$

Recognizing XOR and XNOR properties:

$$A'B' + AB = A XNOR B$$

$$AB' + A'B = A XOR B$$

Substituting these values:

$$D = Bin(A \ XNOR \ B) + Bin'(A \ XOR \ B)$$

Using XNOR identity:

$$D = Bin \oplus (A \oplus B)$$

Thus, the final simplified expression for the difference in a full subtractor is:  $D = (A \oplus B) \oplus Bin$

## Logical expression for borrow

# The **borrow** (**Bout**) **output** is derived as follows:

The basic expression:

$$Bout = A'B'Bin + A'BBin' + A'BBin + ABBin$$

Factoring common terms:

$$Bout = A'Bin(B + B') + A'B(Bin + Bin') + BBin(A + A')$$

Simplifying:

$$Bout = A'Bin + A'B + BBin$$

Alternatively, using another approach:

$$Bout = A'B'Bin + A'BBin' + A'BBin + ABBin$$

Factoring common terms:

$$Bout = Bin(AB + A'B') + A'B(Bin + Bin')$$

Using XOR and XNOR properties:

$$AB + A'B' = A XNOR B$$

Substituting these values:

$$Bout = Bin(A XNOR B) + A'B$$

Using XNOR identity:

$$Bout = Bin (A XOR B)' + A'B$$

Thus, the final simplified expression for borrow in a full subtractor is:

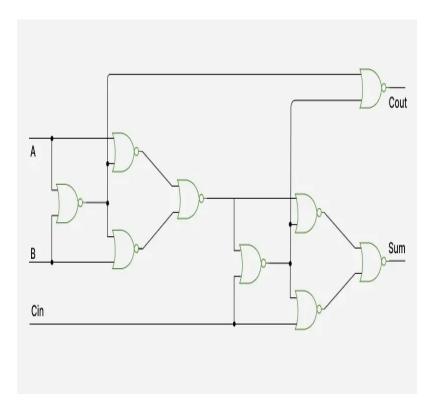

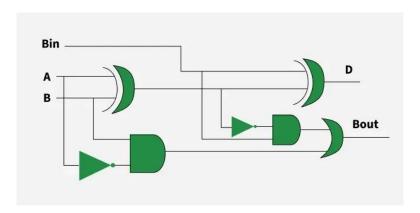

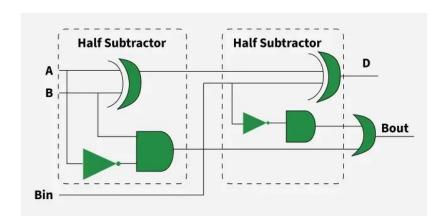

## **Logic Circuit for Full Subtractor:**

## **Implementation of Full Subtractor using Half Subtractors**

2 Half Subtractors and an OR gate is required to implement a Full Subtractor.

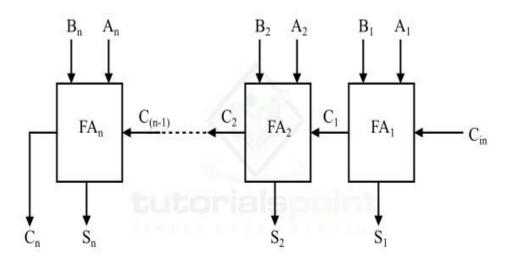

# 2.3. Parallel binary adder:

Parallel adder is a binary adder circuit implemented to add two binary number having N-bits (for example, to add 4-bit binary numbers, we use 4- bit parallel adder, and so on). As its name implies, the parallel adder is a digital combinational circuit that adds two binary numbers in parallel form and generates the arithmetic sum of those binary numbers in parallel form.

As we already mentioned above that a full adder can perform addition of only two one-bit binary numbers consisting of two input bits and one input carry bit, i.e. addition of three bits. But in actual practice, we have to add such binary numbers whose length is more than one bit. To add such binary numbers, we use parallel binary adder which is capable of adding the two binary numbers of any bit length such as 4-bit, 5-bit, etc.

We can implement an N-bit parallel adder with the help of full-adders connected in a chain fashion. The block diagram representation of an N-bit parallel adder using full adders is shown in Figure-2.

Figure 2 - N-Bit Parallel Adder

From the block diagram of the N-bit parallel adder, it can be seen that the carry output from each full-adder is connected to the carry input terminal of the next higher level full-adder in the chain.

The number of full-adder to realize a parallel adder is determined from the number of bits in the two binary numbers to be added. Therefore, an N-bit parallel adder requires N full-adders to perform the addition in parallel form. For example, a 2-bit parallel adder requires 2 full adders, 4-bit parallel adder consists of 4 full adders, and so on.

Operation of N-Bit Parallel Adder Circuit

The working of the N-bit parallel adder shown in figure-2 can be described in the following steps –

- Initially, the full adder  $FA_1$  adds two input bits  $A_1$  and  $B_1$  along with an input carry bit  $C_{in}$ , and it generates the output sum bit  $S_1$  and the carry bit  $C_1$  which is forwarded to the next adder  $(FA_2)$  in the chain. The sum bit  $S_1$  is the least significant bit of the output sum.

- At the next stage, the full adder circuit FA<sub>2</sub> becomes active and adds input bits A<sub>2</sub> and B<sub>2</sub> along with C<sub>1</sub>. It generates the sum bit S<sub>2</sub> which is the second bit of the output sum, and the carry bit C<sub>2</sub> that is connected to the next full adder FA<sub>3</sub> in the chain.

- This process will continue till the last full adder, i.e. FAn in the chain. The full adder uses carry input  $C_{(n-1)}$  to add with the input bits  $A_n$  and  $B_n$  to produce the last bit of the output sum  $S_n$  and the last output carry bit  $C_n$ .

### **Advantages of Parallel Adder:**

Some important advantages of parallel adder are listed below –

- The parallel adder adds bits simultaneously.

- It makes addition of binary numbers fast.

- Parallel adder is more economical.

# **Applications of Parallel Adder:**

The important applications of parallel adders are listed below –

- Parallel adders are used in arithmetic logic units that are used for heavy computing applications.

- Parallel adders are also used in parallel cellular automatic machines for parallel computing.

- Parallel adders are utilized for conversion of BCD into excess-1 code.

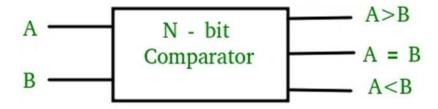

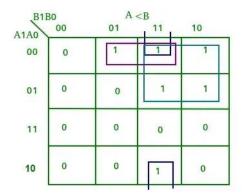

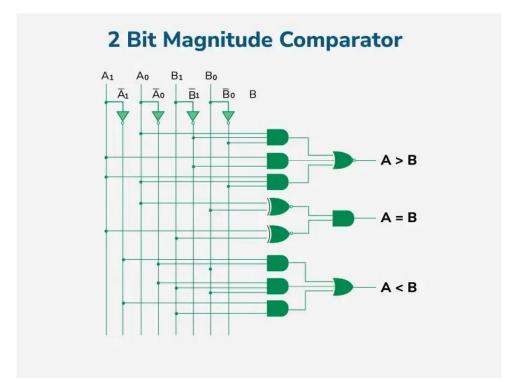

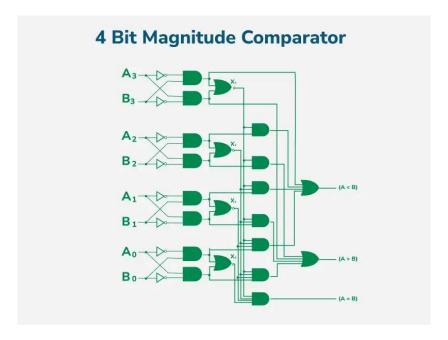

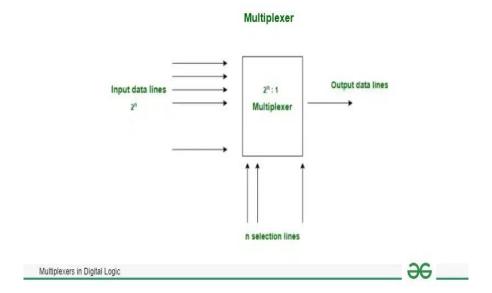

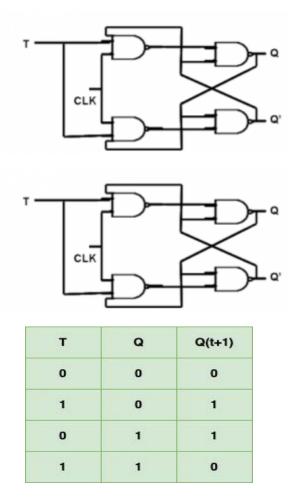

- Parallel adders are also used for the analysis of multiplication algorithms.